Český národní hrdina Jára Zimmerman uvažoval u řešení každého problému o dvou se střídajících fázích:

1- fáze očekávaní

2- fáze zklamání

U Siemensů v padesátých letech minulého století tomu zase říkali:

1- Předprojektové nadšení.

2- Projektové vystřízlivění.

3- Hledání viníků.

4- Potrestání nevinných.

5- Odměna nezůčastněným.

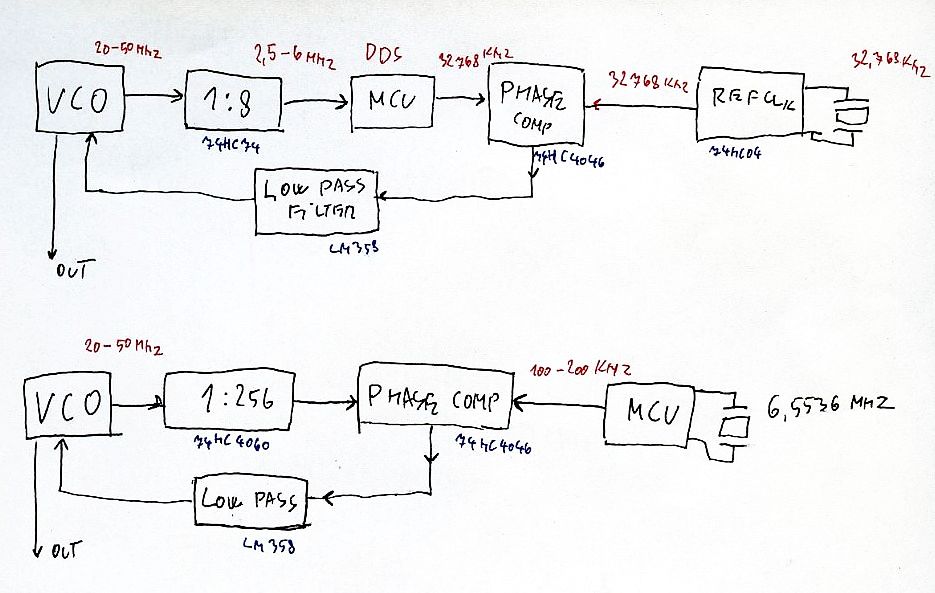

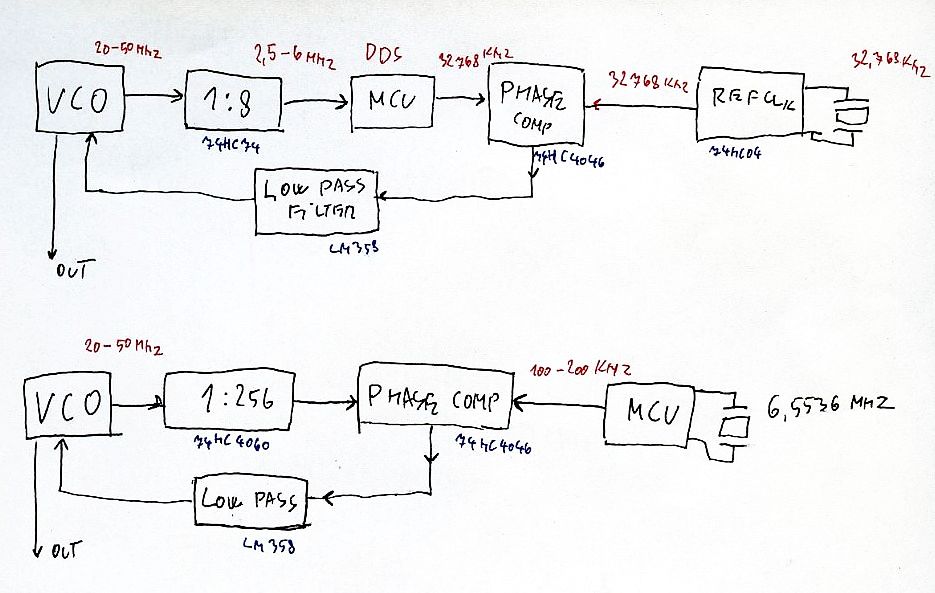

Mám celkem radost, že jste přešel na "mé" řešení (ne že bych měl na něj patent, ale dospěl jsem k němu podobným myšlenkovým pochodem). Radost mám proto, že jsme ke stejnému řešení došli relativně nezávisle na sobě, což znamená, že by principiálně mělo fungovat. Nepočítejte ale, že to bude rozumně fungovat bez A/D převodníku jen s použitím posledního bitu, rozhodně ne na dlouhých vlnách filtr PLL by musel mít příliš dlouhou konstantu, aby odfiltroval (zprůměroval) fázový šum. To už pak můžete rovnou čítat frekvenci oscilátoru vnitřním čítačem AVRka a korigovat ladicí napětí pomocí PWM výstupu (se slušným LC oscilátorem by to mohlo mít stejné a možná i lepší výsledky). Na druhou stranu by mohlo být zajímavé experimentovat s počtem bitů A/D převodu a délkou časové konstanty PLL a pozorovat při tom čistotu spektra (fázový šum a parazitní modulace). Začít s jedním bitem, pak třeba se čtyřmi, šesti, osmi ...

Mimochodem, nemám sice zkušenost s přijímači s frekvenčními syntézami, ale co jsem měl možnost, tak jsem v ničem takovém neceločíselné děliče neviděl, pokud tedy nemyslíte děliče N/N+1, protože ty bych za neceločíselné nepovažoval, výstupní signál z nich je totiž přísně synchronní se vstupním stejně jako u normálního děliče.

Jo, ještě malý dodatek, ten dělič 1:256 za VCO bych dal programovatelný Sežere to sice jeden port navíc, ale zato to dramaticky zvýší frekvenční rozsah syntézy při zachování úzkého rozmezí referenčního signálu pro fázový detektor.

[2]: Pana Kubáče se týká pravděpodobně Cimrmanovské pojetí, neb tři poslední body od Siemensů se ho netýkají. Leda že by se do toho zamontovala paní Kubáčová, viník je jasný, potrestání je na místě, jelikož se pan Kubáč ukájí nad AVRkem místo toho, aby se ukájel nad paní Kubáčovou, no a odměnu si nezúčastněná paní Kubáčová vybere až si zklamaný a sexuálně frustrovaný (z nefungující onanie nad AVR) pan Kubáč se sklopenýma ušima a vztyčeným přirozením půjde pokorně lehnout na manželské lože :-). Panu Kubáčovi se omlouvám pokud ho tento nejapný pokus o žert urazil, má možnost použít svá administrátorská práva a příspěvek promptně smazat.

[3]: Nemohu si pomoct, ale cyklus N+1 děličky v PLL mi připadá delší než cyklus N - díky tomu je ladící napětí smyčky "někde mezi" a díky tomu kmitá VCO mimo rastr daný referenčním kmitočtem

Jediný rozdíl proti použití nejvyššího bitu DDS vidím v tom, že u DDS je výrazně hůře predikovatelné, který cyklus bude o 1 takt kratší a který bude delší - parazitní modulace jsou "více rozplizlé" - což může ale nemusí být výhoda

Jinak použítí ring oscilátorů je velice zajímavé - oscilátor s 3 hradly má výrazně větší jiteer než oscilátor s 5 hradly a se 7 a více by to asi bylo zase lepší - proto si myslím, že třeba PLL v procesorech mají ring oscilátor z nějakého velkého lichého počtu hradel a jitter vůbec neřeší

Už mám nakresleno schémátko kde místo LC oscilátoru je ring oscilátor z 5 hradel typu 74AC - se zpoždením 3ns - měl by se chovat výrazně lépe než PLL ze 3 hradel typu 74HC

http://petr-kubac.blog.cz/1404/vidlakovo-elektro-75-kvadraturni-generator

která se ale taky "pod knutou" PLL nechová úplně špatně

Zdá se mi, že výšeuvedený siemensácký algoritmus nemilosrdně chodí jak na ring-oscilátor z hradel řízený PLL v kontaktním poli, tak třeba i na fosfolipidy profesora Holého. Je pak už jen naprosto nepodstatné, zdali podle bodu č.5 bakšiš nakonec dostane ostravská GME, a nebo ústav organické chemie z Prahy...

[5]: Ne ne, cyklus N+1 děličky je pořád v rytmu vstupního signálu, tedy pokud oba myslíme použití dual modulus prescaler

http://en.wikipedia.org/wiki/Dual-modulus_prescaler

Celý vtip je v tom, že při použití předděličky N+1/N se celá PLL tváří jako kdyby tam žádná předdělička nebyla a programovatelný čítač čítal přímo frekvenci VCO. Čítání se ovšem pořád děje přísně v rámci počtů period (rastru) VCO k žádnému neceločíselnému dělení nedochází.

U použití jednoho bitu DDS mám velké obavy z "aliasingu" budou totiž existovat frekvence, u kterých se okamžik překlopení nejvyššího bitu DDS bude jen pomalu pohybovat oproti rastru VCO a PLL pak bude "dýchat" v rytmu tohoto aliasingu. I kdyby ale byl jitter DDS náhodný pořád je odstup šumu ladicího napětí daný poměrem časové konstanty filtru ke kvantování DDS a pokud je to např. 100ms/1,53us, bude šum ladicího napětí řádově v desítkách uV, což při citlivosti VCO řádově 10MHz/V způsobí parazitní modulaci se zdvihem ve stovkách Hz a to je na úzkopásmových provozech určitě slyšet, když jsou šířky kanálů v desítkách kHz.

Ring oscilátor s více hradly bude mít menší jitter pravděpodobně kvůli nižžší frekvenci a tím delší době na ustálení stavu hradla. Hradlo se pak překlápí z lépe definovaného stavu a není tak citlivé na vnější vlivy a šumy. Rozhodně je lepší použít více rychlých hradel, než menší počet pomalých. Celkem zajímavá je i synchronizace ring oscilátoru s krystalem, když se oscilátor vtáhne do synchronizace, má celkem dobrou stabilitu a lze přelaďovat až ve třetím řádu, chová se to jako lepší LC oscilátor.

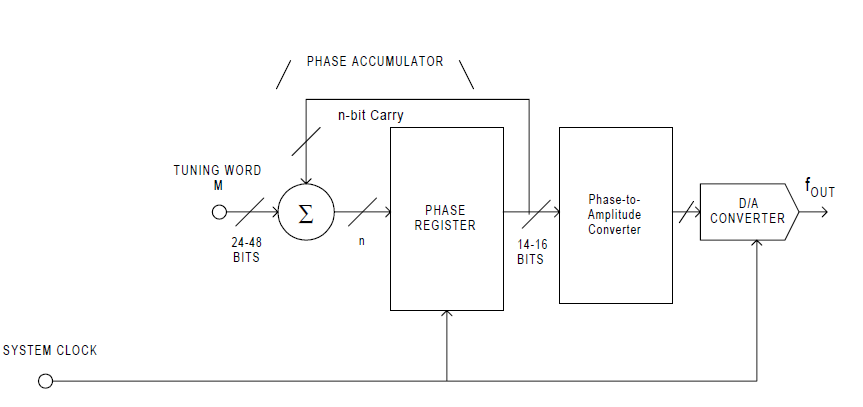

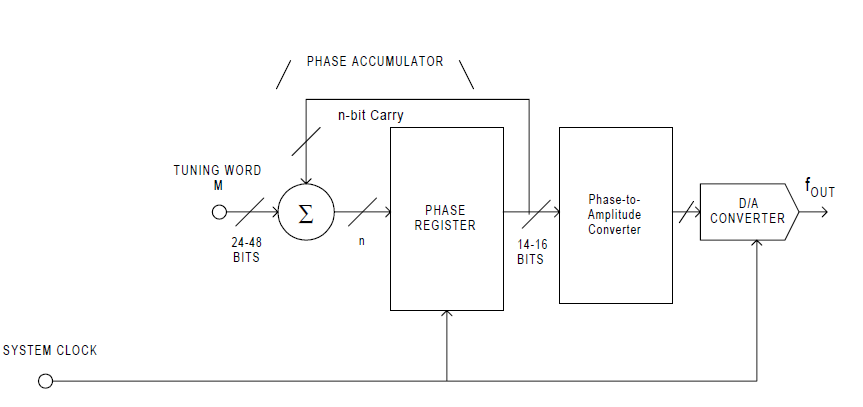

[7]: Zdá se že můj "myšlenkový model byl špatný" - nicmnéně jsem narazil na aplikační poznámku od TI o frakčních - neceločíselných PLL - jakoby opisovali ode mně (nebo já od nich) - první level je dual modulus dělič, jehož dělící poměr mezi N a N+1 přepíná fázový akumulátor ve stylu DDS ;-)

Aby kompenzovali parazitní modulace tak "fázové zbytky" po přetečení fázového akumulátoru cpou do ladícího napětí VCO - zajímavá idea zavánějící škrábáním levou rukou za pravým uchem.

Jo - a nepřítomnost neceločíselných PLL ve vaší realitě ? Máte v kapse mobil ? ;-))

[8]: Myslím, že váš myšlenkový model až tak špatný nebyl, jen trpí stejnými neduhy jako frakční PLL, hlavně co se týče rušivých spektrálních čar v oblasti propustnosti PLL filtru (to co jsem nazval "aliasingem"). Tenhle nedostatek se dá opravit buď vygenerovaným analogovým signálem v protifázi rušivých složek (frakční PLL druhého řádu), nebo pomocí sigma-delta modulátoru (frakční PLL třetího řádu).

Váš nápad s DDS bez A/D převodníku by šel za cenu dalšího strojového času (prodloužení smyčky DDS) doplnit o softwarovou sigma-delta modulaci (bohužel asi jen prvního řádu), čímž by mohlo dojít k částečné redukci rušivých složek. Otázka je, jestli to stojí za vynechání jednoho A/D převodníku, který by se dal postavit i z odporové sítě pověšené na port AVR (kdysi osobně vyzkoušeno na LPT portu a i s obyčejnými odpory je chyba pod půl LSB). I když s A/D převodníkem dojde k razantnímu zlepšení, přeci jen i v DDS jsou přítomny rušivé šumy, 8 bitů je málo, většinou se používají 10 a více bitové převodníky, ale pořád je 8 bitů víc než jeden. No a 24 stejných odporů na osmibitovou síť R2R snad mají i ve vidlákově. Taky jsem kdysi uvažoval o TDA1545A pověšené na SPI rozhraní, zvůádá až 192ksamplů, takže by řekněme 20kHz referenční signál pro PLL zvládla a 16 bitů už je slušných. TDA1545 bývala v každé CD mechanice, kterých se ve sberných dvorech musí válet vagony.

Tipl bych si, že pan Kubáč je Vodnář (a nebo má aspoň ascendent v tomto znamení).